1. Функциональное описание

Операции чтения и записи в SDRAM пакетно-ориентированные; доступ начинается с выбранного места и продолжается для запрограммированного количества ячеек в запрограммированной последовательности. Доступ начинается с команды активизации ACTIVE, за которой следует команда чтения READ или записи WRITE. Биты адреса, защёлкнутые во время команды ACTIVE, используются для выбора банка и ряда, к которым будет производиться доступ (BA0 и BA1 выбирают банк, A0-A11 выбирают ряд). Биты адреса, защёлкнутые во время команды READ или WRITE, используются при выборе начального адреса колонки для пакетного доступа.

Перед нормальной работой SDRAM должна быть инициализирована. В следующих разделах приведены детальная информация об инициализации устройства, описание регистра, описания команд и работа устройства.

2. Инициализация

Подача питания на SDRAM и её инициализация должны производиться строго заданным образом. В противном случае устройство может работать неправильно. После подачи питания на Vdd и VddQ (одновременно) и установления тактовой частоты (установившаяся тактовая частота определяется как циклический сигнал с временными ограничениями, заданными для тактового входа), SDRAM требует паузы в 100 мкс перед подачей любой команды, кроме COMMAND INHIBIT или NOP. От начала и до конца этого периода в 100 мкс должна быть приложена одна из этих команд.

Затем должна быть подана команда деактивации (PRECHARGE). Все банки будут деактивированы, и, таким образом установлены в пассивное (idle) состояние.

После перехода в пассивное состояние должны быть выполнены два цикла автоматической регенерации AUTO REFRESH. После этого SDRAM готова к программированию регистра управления. Поскольку после включения питания регистр управления устанавливается в неопределённое состояние, он должен быть загружен до выполнения любой операционной команды.

3. Описание регистра

3.1. Регистр управления

Регистр управления используется для определения конкретного режима работы SDRAM. Это определение включает выбор длины пакета, типа пакета, задержки CAS, режима работы и режима записи пакета, как показано на рис. 1. Регистр управления программируется через команду загрузки регистра управления LOAD MODE REGISTER и сохраняет записанную информацию до следующего программирования или до выключения питания.

Биты M0-M2 регистра управления задают длину пакета. M3 задаёт тип пакета (последовательный или чередующийся), M4-M6 задают задержку CAS, M7 и M8 определяют режим работы, M9 задаёт режим записи пакета, и M10 и M11 зарезервированы для будущего использования.

Регистр управления должен загружаться, когда все банки находятся в пассивном состоянии, и контроллер должен выдержать заданную задержку перед началом следующей операции. Нарушение этого требования приведёт к неправильной работе.

3.2. Длина пакета

Доступ к SDRAM по чтению и по записи пакетно-ориентированный, при этом длина пакета программируется, как показано на рис. 1. Длина пакета определяет максимальное число ячеек, которые могут быть доступны для поданной команды чтения или записи. Пакеты длиной 1, 2, 4 или 8 слов могут быть последовательными или чередующимися, а полностраничный пакет может быть только последовательным. Полностраничный пакет используется совместно с командой окончания пакета BURST TERMINATE, чтобы получить произвольную длину пакета.

Зарезервированные состояния использовать нельзя, чтобы не получить несовместимость с будущими версиями.

При подаче команды чтения или записи выбирается блок ячеек колонки, равный длине пакета. Все ячейки для этого пакета размещаются в пределах этого блока. Это означает, что если будет достигнута граница блока, то пакет вернётся к его началу. Блок однозначно выбирается линиями A1-A9 (x4), A1-A8 (x8) или A1-A7 (x16), когда длина пакета равна 2; A2-A9 (x4), A2-A8 (x8) или A2-A7 (x16), когда длина пакета равна 4; и A3-A9 (x4), A3-A8 (x8) или A3-A7 (x16), когда длина пакета равна 8. Оставшиеся младшие значащие биты используются для выбора стартового адреса в блоке. Полностраничный пакет при достижении границы возвращается к началу страницы. (Full-page bursts wrap within the page if the boundary is reached.)

3.3. Тип пакета

Таблица 1. Определение пакета

Доступ внутри пакета может быть запрограммирован как последовательный или чередующийся. Это называется типом пакета и выбирается через бит M3.

Порядок доступа внутри пакета определяется длиной пакета и стартовым адресом колонки, как показано в таблице 1.

Обратите внимание:

1. Для полностраничного доступа: y=1,024(x4); y=512(x8); y=256(x16).

2. Для пакета длиной 2 слова A1-A9(x4), A1-A8(x8) или A1-A7(x16) выбирают блок из двух слов; A0 выбирает начальную колонку в блоке.

3. Для пакета длиной 4 слова A2-A9(x4), A2-A8(x8) или A2-A7(x16) выбирают блок из четырёх слов; A0-A1 выбирают начальную колонку в блоке.

4. Для пакета длиной 8 слов A3-A9(x4), A3-A8(x8) или A3-A7(x16) выбирают блок из восьми слов; A0-A2 выбирают начальную колонку в блоке.

5. Для полностраничного пакета выбирается весь ряд и A0-A9(x4), A0-A8(x8) или A0-A7(x16) выбирают всю начальную колонку.

6. Когда в описанной выше последовательности достигается граница блока, следующий доступ производится к началу блока.

7. Для пакета длиной в один блок A0-A9(x4), A0-A8(x8) или A0-A7(x16) выбирают единственную колонку и M3 игнорируется.

3.4. Задержка CAS

Задержка CAS – это

измеряемый в тактах промежуток между подачей команды чтения и доступностью первой

порции выходных данных. Задержка может быть установлена равной двум или трём тактам.

Задержка CAS – это

измеряемый в тактах промежуток между подачей команды чтения и доступностью первой

порции выходных данных. Задержка может быть установлена равной двум или трём тактам.

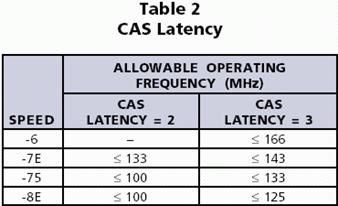

Если команда чтения подаётся на тактовом перепаде n и задержка составляет m тактов, то данные будут доступны на тактовом перепаде n+m. Линии данных начнут управляться на такт раньше (n+m-1) и, если были выдержаны соответствующие времена доступа, то данные установятся на тактовом перепаде n+m. Например, предположим, что тактовый период такой, что все времена доступа выдерживаются. Если команда чтения подаётся в момент T0 и запрограммирована задержка в два такта, линии данных начнут управляться в момент T1 и данные установятся в момент T2, как показано на рис.2. В таблице 2 показаны рабочие частоты, при которых может быть использована каждая из установок задержки CAS.

Зарезервированные состояния не должны использоваться во избежание неизвестных операций или несовместимости в будущем.

3.5. Рабочий режим

Нормальный рабочий режим выбирается установкой M7 и M8 в 0. Другие комбинации значений M7 и M8 зарезервированы для будущего использования и/или тестовых режимов. Запрограммированная длина пакета действительна как для пакетов чтения, так и для пакетов записи.

Тестовые режимы и зарезервированные состояния не должны использоваться во избежание неизвестных операций и несовместимости с будущими версиями.

3.6. Режим пакетной записи

Когда M9=0, длина пакета, запрограммированная через M0-M2, действительна и для пакетов чтения, и для пакетов записи. Когда M9=1, запрограммированная длина действительна только для пакетов чтения, а запись осуществляется только в отдельные ячейки (не пакетный доступ).

4. Команды

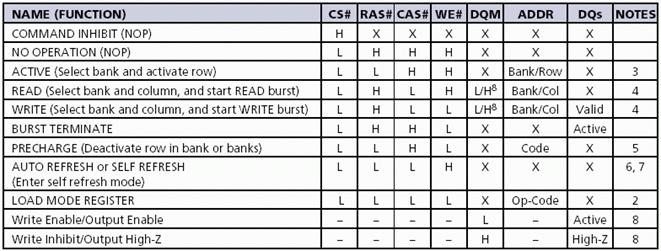

В таблице истинности 1 приведён обзор доступных команд. Затем следует описание каждой команды. После раздела описания работы появляются три дополнительные таблицы истинности. В них приводится информация о предшествующих/следующих состояниях.

Таблица истинности 1. Команды и операции DQM

Обратите внимание:

1. Для всех показанных команд, кроме SELF REFRESH, на CKE высокий уровень.

2. A0-A11 определяют операционный код, записанный в регистр управления.

3. A0-A11 задают адрес ряда, и BA0, BA1 определяют, какой банк сделан активным.

4. A0-A9(x4), A0-A8(x8) или A0-A7(x16) формируют адрес колонки. Высокий уровень на A10 разрешает автоматическую деактивацию (не постоянно). Низкий уровень на A10 запрещает автоматическую деактивацию. BA0, BA1 определяют, в какой банк будет производиться запись или из какого – чтение.

5. Низкий уровень на A10 и BA0, BA1 определяет, что банк будет деактивирован. При высоком уровне на A10 все банки будут деактивированы независимо от BA0, BA1.

6. Это команда автоматической регенерации AUTO REFRESH, если на CKE высокий уровень, и саморегенерации SELF REFRESH, если низкий.

7. Внутренний счётчик регенерации управляет адресацией рядов. Состояние всех входов и линий ввода-вывода, кроме CKE, безразлично.

8. Активация и деактивация линий данных во время записи (нулевая задержка) и чтения (задержка в два такта).

4.1. Запрет команды (COMMAND INHIBIT)

Функция COMMAND INHIBIT предотвращает выполнение устройством SDRAM новой команды независимо от того, что разрешён тактовый сигнал. SDRAM фактически не выбрана. На уже выполняющиеся операции это не влияет.

4.2. Нет операции (NOT OPERATION, NOP)

Команда NOT OPERATION (NOP) используется для выполнения пустой операции, когда SDRAM выбрана (на CS низкий уровень). Это предохраняет от выполнения нежелательных команд во время пассивного состояния или ожидания. На уже выполняющиеся операции это не влияет.

4.3. Загрузка регистра управления (LOAD MODE REGISTER)

Регистр управления загружается через входы A0-A11. См. заголовок регистра управления в разделе описания регистра. Команда LOAD MODE REGISTER может подаваться только тогда, когда все банки находятся в пассивном состоянии, и следующая исполняемая команда не может быть подана до истечения интервала времени tMRD.

4.4. Активация (ACTIVE)

Команда активации ACTIVE используется, чтобы открыть (или активизировать) ряд в отдельном банке для последующего доступа. Значения на входах BA0, BA1 выбирают банк, и адрес, поданный на A0-A11, выбирает ряд. Этот ряд остаётся активным (или открытым) для доступа до поступления команды PRECHARGE для этого банка. Команда PRECHARGE должна быть перед открытием другого ряда этого же банка.

4.5. Чтение (READ)

Команда чтения используется, чтобы начать чтение пакета из активного ряда. Значения на входах BA0, BA1 выбирают банк, и адрес на входах A0-A9(x4), A0-A8(x8) и A0-A7(x16) выбирают начальную колонку пакета. Сигнал на входе A10 определяет, будет ли использоваться автоматическая деактивация. Если выбрана автоматическая деактивация, ряд, из которого производится чтение, будет деактивирован после чтения пакета. Если она не выбрана, ряд будет оставаться открытым для последующего доступа. Чтение данных, появляющихся на линиях данных, зависит от логического уровня на входах DQM, поданного на два такта до того. Если сигнал DQM имеет высокий уровень, то через два такта линии данных будут в состоянии высокого импеданса. Если сигнал DQM имеет низкий уровень, то на линиях данных будут правильные данные.

4.6. Запись (WRITE)

Команда записи используется, чтобы начать запись пакета в активный ряд. Значения на входах BA0, BA1 выбирают банк, и адрес на входах A0-A9(x4), A0-A8(x8) и A0-A7(x16) выбирают начальную колонку пакета. Сигнал на входе A10 определяет, будет ли использоваться автоматическая деактивация. Если выбрана автоматическая деактивация, ряд, в который производится запись, будет деактивирован после чтения пакета. Если она не выбрана, ряд будет оставаться открытым для последующего доступа. Входные данные, появляющиеся на линиях данных, будут записываться в массив памяти в соответствии с состоянием входов DQM в момент появления данных. При низком уровне на DQM соответствующие данные будут записаны в память. При высоком уровне соответствующие данные будут игнорироваться и запись в этот байт/колонку не произойдёт.

4.7. Деактивация (PRECHARGE)

Команда PRECHARGE используется для деактивации открытого ряда в отдельном банке или открытого ряда во всех банках. Банк(и) будет открыт для последующего доступа по истечении заданного времени (tRP) после подачи команды PRECHARGE. Вход A10 определяет, будет деактивирован один банк или все сразу. Если деактивируется только один банк, то линии BA0, BA1 определяют, какой именно. В противном случае состояние BA0, BA1 безразлично. С момента деактивации банк находится в пассивном состоянии и должен быть активирован перед любой командой чтения или записи для этого банка.

4.8. Автоматическая деактивация (AUTO PRECHARGE)

Автоматическая деактивация позволяет деактивировать отдельный банк без использования явно поданной команды. Это достигается использованием линии A10 для разрешения автоматической деактивации в сочетании с командами чтения или записи. Деактивация банка/ряда, который адресуется командой чтения или записи, автоматически происходит по окончании пакета чтения или записи, за исключением полностраничного пакетного режима, при котором автоматическая деактивация не применяется. Режим автоматической деактивации не постоянен и разрешается или сбрасывается для каждой отдельной команды записи или чтения.

Автоматическая деактивация гарантирует, что деактивация произойдёт, на ранней стадии выполнения пакета. Пользователь не должен подавать других команд для этого банка до истечения времени деактивации tRP. Это определяется, как если бы команда PRECHARGE была подана явно несколько ранее, как показано в разделе описания работы в этом документе.

4.9. Окончание пакета (BURST TERMINATE)

Команда окончания пакета используется, чтобы укорачивать пакеты фиксированной длины или полностраничные пакеты. Выполнение последних полученных команд чтения или записи будет прервано этой командой, как показано в разделе описания работы в этом документе.

4.10. Автоматическая регенерация (AUTO REFRESH)

Автоматическая регенерация используется во время нормальной работы SDRAM и аналогична регенерации CAS-BEFORE-RAS в обычной DRAM. Эта команда не постоянна, её надо подавать каждый раз, когда требуется регенерация. Перед её выполнением все активные банки должны быть деактивированы. Команда AUTO REFRESH должна быть подана не менее, чем за время tRP после команды PRECHARGE, как показано в разделе описания работы.

Адресация производится встроенным контроллером регенерации. Поэтому при автоматической регенерации состояние адресных входов безразлично. 64 Мб SDRAM требует 4096 циклов автоматической регенерации каждые 64 мс (tREF) независимо от ширины слова. Выполнение команды автоматической регенерации каждые 15625 мкс необходимо и достаточно для полной регенерации всех рядов. В качестве альтернативы 4096 команд автоматической регенерации могут выполняться одним пакетом с минимальным временем цикла tRC каждые 64 мс.

4.11. Саморегенерация (SELF REFRESH)

Команда саморегенерации может быть использована для сохранения данных в SDRAM, даже если система находится в состоянии пониженного энергопотребления. В этом режиме SDRAM сохраняет данные без внешнего тактирования. Команда саморегенерации выполняется аналогично команде автоматической регенерации, за исключением того, что CKE запрещена (низкий уровень). При подаче команды саморегенерации состояние всех входов SDRAM безразлично, за исключением CKE, на котором должен быть низкий уровень.

В режиме саморегенерации SDRAM вырабатывает собственную внутреннюю тактовую частоту, при помощи которой выполняются внутренние циклы автоматической регенерации. SDRAM должна находиться в режиме саморегенерации не менее tRAS и может находиться в нём неопределённо долго.

Процедура выхода из режима саморегенерации требует выполнения последовательности команд. Сначала должна стабилизироваться тактовая частота, перед тем, как на CKE будет установлен высокий уровень. После подачи высокого уровня на CKE надо подавать команду NOP в течение не менее двух тактовых циклов для завершения внутренних процессов регенерации.

После выхода из режима саморегенерации команда автоматической регенерации должна подаваться каждые 15625 мс или менее, так как и при саморегенерации, и при автоматической регенерации используется один счётчик рядов.

5. Работа

5.1. Активация банка/ряда

Перед подачей команды чтения или записи для банка SDRAM ряд в этом банке должен быть «открыт». Это обеспечивается

при помощи команды ACTIVE, которая одновременно выбирает

и активизирует банк и ряд (см. рис. 3).

Перед подачей команды чтения или записи для банка SDRAM ряд в этом банке должен быть «открыт». Это обеспечивается

при помощи команды ACTIVE, которая одновременно выбирает

и активизирует банк и ряд (см. рис. 3).

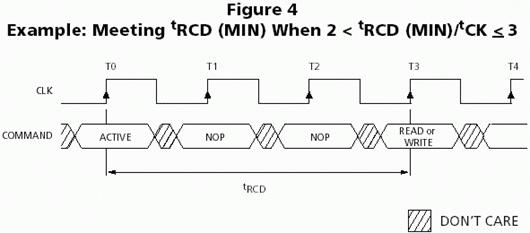

После открытия ряда (командой ACTIVE) можно подавать команду чтения или записи для этого ряда с учётом времени tRCD. tRCD (MIN) надо разделить на период тактовой частоты и округлить до ближайшего большего целого числа, чтобы определить ближайший тактовый перепад после команды активизации, на котором можно подавать команду записи или чтения. Например, для tRCD=20нс и тактовой частоты 125 МГц (период 8 нс) получим результат 2,5 тактов и округлим до 3. Это проиллюстрировано на рис. 4, который подходит для всех случаев, когда 2 < tRCD (MIN) / tCK =< 3. (Эта же процедура применяется для преобразования других временных ограничений из наносекунд в такты.)

Следующая команда активации для другого ряда этого же банка может быть подана в момент, когда доступ к первому банку ещё не закончен. В результате получается сокращение общего времени доступа. Минимальный промежуток времени между последовательными командами ACTIVE определяется величиной tRRD.

5.2. Чтение

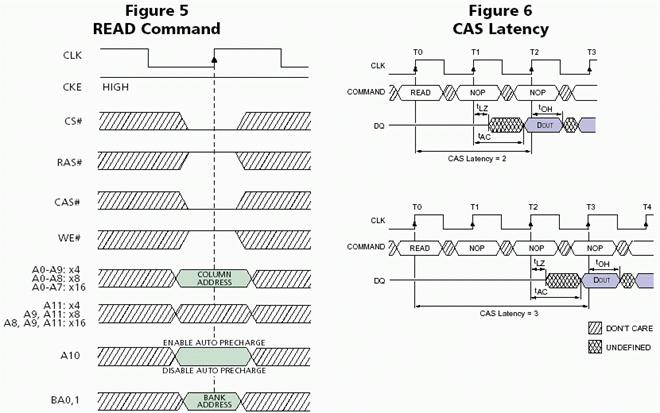

Пакеты чтения запускаются командой чтения READ, как показано на рис.5.

Адреса стартовой колонки и банка поступают с командой чтения. При этом автоматическая деактивация разрешается или запрещается только для текущего пакета. Если автоматическая деактивация разрешена, ряд, к которому производится доступ, будет деактивирован по окончании пакета. Для команд чтения в следующих примерах автоматическая деактивация запрещена.

В пакетах чтения правильные выходные данные из стартовой колонки будут доступны через промежуток времени CAS latency после команды чтения. Каждый следующий элемент данных будет доступен на следующем положительном перепаде тактового импульса. На рис. 6 показана временная диаграмма для каждого возможного значения CAS latency.

За пакетом чтения фиксированной длины может следовать (или прерывать его) команда деактивации этого же банка (при условии, что автоматическая деактивация не разрешена), и полностраничный пакет может быть прерван командой деактивации для того же банка. Команда деактивации должна подаваться за x циклов до тактового перепада, на котором появится последний желаемый элемент данных, где x равен задержке CAS минус 1. Это показано на рис. 11 для каждой возможной задержки CAS. Элемент данных x+3 – это последний элемент пакета из четырёх слов или последний требуемый из длинного пакета. Команда для текущего банка, следующая за командой деактивации, не может быть подана раньше, чем через время tRP. Обратите внимание, что часть времени деактивации ряда скрыта во времени доступа к последнему элементу (элементам) данных.

Когда пакет фиксированной длины выполняется целиком, команда деактивации, поданная в оптимальный момент, даёт такой же результат, как если бы пакет той же самой фиксированной длины выполнялся с автоматической деактивацией. Недостатком отдельной подачи команды PRECHARGE является необходимость того, чтобы шины команды и адреса были доступны в заданное время для подачи команды. Преимуществом же является то, что её можно использовать для прерывания пакета фиксированной длины или полностраничного пакета.

Полностраничный пакет чтения может быть прерван командой прерывания пакета BURST TERMINATE. Пакет фиксированной длины также может быть прерван этой командой, при условии, что автоматическая деактивация не включена. Команда прерывания пакета должна быть подана за x тактов до тактового перепада, на котором появляется последний требуемый элемент данных, где x равен задержке CAS минус 1. Это показано на рис. 12 для каждой возможной задержки CAS. Элемент данных x+3 – это последний требуемый элемент данных длинного пакета.

5.3. Запись

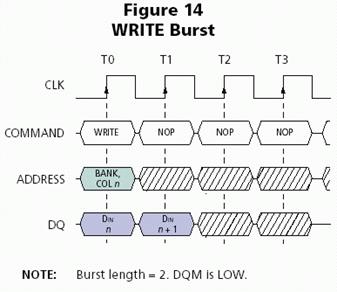

Пакеты записи запускаются командой записи WRITE, как показано на рис. 13.

Пакеты записи запускаются командой записи WRITE, как показано на рис. 13.

Адреса стартовой колонки и банка поступают с командой записи, и автоматическая деактивация может быть во время этого доступа разрешена или запрещена. Если автоматическая деактивация разрешена, ряд, к которому производится доступ, деактивируется по окончании пакета. Для команд записи, использованных в следующих иллюстрациях, автоматическая деактивация запрещена.

Во время пакетов записи первый правильный элемент входных данных поступает одновременно с командой записи. Следующий элемент данных записывается при каждом следующем положительном перепаде тактового импульса. После завершения пакета фиксированной длины, если не подаются никакие другие команды, линии данных остаются в состоянии высокого импеданса и следующие входные данные будут игнорироваться (см. рис. 14). Полностраничный пакет будет продолжаться, пока его не прервут. (В конце страницы он вернётся к нулевой колонке и продолжится.)

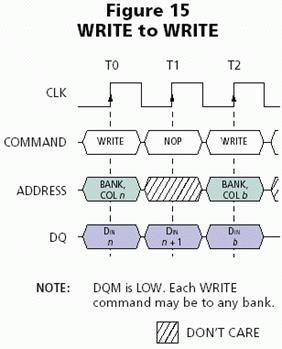

Данные для любого пакета записи могут быть прерваны следующей командой записи, и за данными пакета фиксированной длины могут непосредственно следовать данные для другой команды записи. Новая команда записи может быть подана на любом такте, следующем за первой командой записи, и данные, поступившие одновременно с новой командой, используются для этой новой команды.

Пример показан на рис. 15. Данные n+1 – это последние данные пакета из двух слов или последние требуемые данные длинного пакета. 64 Мб SDRAM используют конвейерную архитектуру и не требуют выполнения правила 2n, свойственного старым архитектурам. Команда записи может подаваться на любом тактовом цикле, следующем за предыдущей командой записи. Полноскоростной произвольный доступ по записи внутри страницы может быть выполнен к этому же банку, как показано на рис. 16, или же каждая последующая запись может выполняться в другой банк.

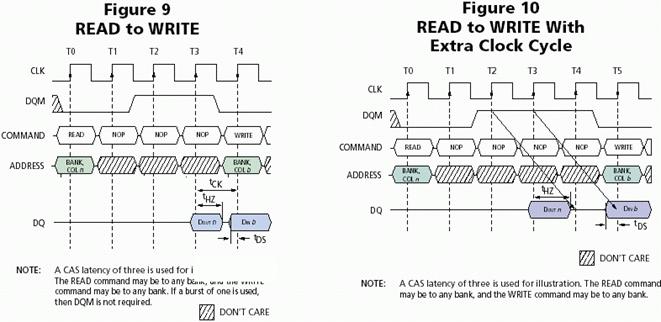

Данные для любого пакета записи могут быть прерваны

последующей командой чтения, и за данными для пакета записи фиксированной длины

могут непосредственно следовать данные последующей команды чтения. Во время подачи

команды чтения последующие данные игнорируются, и запись не выполняется. Пример

показан на рис. 17. Данные n+1

– это последние данные пакета из двух слов или последние требуемые данные

длинного пакета.

Данные для любого пакета записи могут быть прерваны

последующей командой чтения, и за данными для пакета записи фиксированной длины

могут непосредственно следовать данные последующей команды чтения. Во время подачи

команды чтения последующие данные игнорируются, и запись не выполняется. Пример

показан на рис. 17. Данные n+1

– это последние данные пакета из двух слов или последние требуемые данные

длинного пакета.

За данными для пакета фиксированной длины может следовать (или прерывать их) команда деактивации для этого же банка (при условии, что автоматическая деактивация не включена), и полностраничный пакет может быть прерван командой деактивации для этого же банка. Команда деактивации должна подаваться через tWR после тактового перепада, на котором поступает последний требуемый элемент данных. Режим автоматической деактивации требует tWR плюс один такт времени, независимо от частоты. Кроме того, когда прерывается пакет записи, должен использоваться сигнал DQM для того, чтобы маскировать входные данные за такт до того и на том же такте, что и команда деактивации. Пример показан на рис. 18. Данные n+1 – это последние данные пакета из двух слов или последние требуемые данные длинного пакета. Следующая команда после PRECHARGE для этого же банка должна подаваться не менее, чем через tRP.

По окончании пакета фиксированной длины команда деактивации, выполненная

в оптимальный момент времени, производит тот же эффект, как если бы этот пакет

фиксированной длины выполнялся с автоматической деактивацией. Недостатком

отдельной подачи команды PRECHARGE является

необходимость того, чтобы шины команды и адреса были доступны в  заданное

время для подачи команды. Преимуществом же является то, что её можно использовать

для прерывания пакета фиксированной длины или полностраничного пакета.

заданное

время для подачи команды. Преимуществом же является то, что её можно использовать

для прерывания пакета фиксированной длины или полностраничного пакета.

Пакет записи фиксированной длины или полностраничный пакет может быть прерван командой BURST TERMINATE. Когда прерывается пакет записи, то данные, поступающие одновременно с командой прерывания, игнорируются. Последними записанными данными (при условии низкого уровня на DQM) будут данные, поступившие на предыдущем такте перед подачей команды прерывания. Это показано на рис. 19, где данные n – это последний требуемый элемент данных длинного пакета.

5.4.

Деактивация (PRECHARGE)

Деактивация (PRECHARGE)

Команда деактивации (рис. 20) используется для деактивации открытого ряда в отдельном банке или открытого ряда во всех банках. Банк(и) будет доступен для обращения к следующему ряду через некоторое заданное время tRP, прошедшее после подачи команды деактивации. Вход A10 определяет, будет ли деактивирован один банк или все, и если один, то входы BA0, BA1 выбирают банк. Когда все банки деактивированы, состояние входов BA0, BA1 безразлично. После деактивации банк находится в пассивном (idle) состоянии и должен быть активирован перед любой предназначенной для него командой чтения или записи.

5.5. Отключение (Power-Down)

Отключение происходит, если на CKE подан низкий уровень одновременно с командами NOP или COMMAND INHIBIT в отсутствие обращения. Если отключение происходит, когда все банки находятся в пассивном состоянии (idle), то этот режим называется неактивным отключением (precharge power-down). Если отключение происходит, когда активен ряд в одном из банков, то такой режим называется активным отключением (active power-down).При отключении деактивируются все входные и выходные буфера, за исключением CKE, для максимальной экономии энергии. Устройство не может оставаться в таком состоянии дольше периода регенерации (64 мс), так как в этом режиме регенерация не осуществляется.

Выход из состояния отключения производится подачей команды NOP или COMMAND INHIBIT и высокого уровня на CKE на требуемом тактовом перепаде (через tCKS). См. рис. 21.

5.6. Приостановка тактов (CLOCK SUSPEND)

Приостановка тактов происходит, когда выполняется доступ к колонке/пакет и на CKE подаётся низкий уровень. В режиме приостановки тактов внутренний тактовый сигнал деактивируется, «замораживая» синхронную логику.

Для каждого положительного тактового перепада, при котором на CKE низкий уровень, следующий внутренний положительный тактовый перепад приостановлен. Любые команды и данные, появляющиеся на входных выводах во время приостановленного внутреннего тактового перепада, игнорируется, любые данные на выводах данных удерживаются и счётчики пакетов не инкрементируются, пока такты приостановлены. (См. примеры на рис. 22 и 23.)

Выход из режима приостановки тактов осуществляется путём подачи высокого уровня на CKE. Внутреннее тактирование и связанные с ним операции возобновляются на следующем положительном тактовом перепаде.

5.7. Пакетное чтение/одиночная запись

Режим пакетного чтения/одиночной записи устанавливается через установку единицы в бите режима пакетной записи M9 регистра управления. В этом режиме все команды записи вызывают запись только одной ячейки (единичный пакет), независимо от запрограммированной длины пакета. Команды чтения выполняются в соответствии с запрограммированной длиной пакета, как и при нормальной работе (M9=0).

5.8. Параллельная автоматическая деактивация (CONCURRENT AUTO PRECHARGE)

Команды доступа (чтения или записи) к другому банку во время выполнения команды доступа с разрешённой автоматической деактивацией не допускаются в SDRAM, если она не поддерживает режим параллельной автоматической деактивации. SDRAM фирмы Micron поддерживают этот режим. Четыре варианта использования этого режима описаны ниже.

5.8.1.Чтение с автоматической деактивацией

5.8.1.1. Прерванное чтением (с автоматической деактивацией или без)

Чтение банка m прерывает чтение банка n с задержкой на CAS latency. Деактивация банка начнётся, когда будет подана команда чтения для банка m (рис. 24).

5.8.1.2. Прерванное командой записи (с автоматической деактивацией или без)

Запись в банк m прервёт чтение из банка n. За два такта до этого должно быть сделано DQM, чтобы предотвратить состязания на шине. Деактивация банка n начнётся, когда будет подана команда записи в банк m (рис. 25).

5.8.2.Запись с автоматической деактивацией

5.8.2.1. Прерывается чтением (с автоматической деактивацией или без неё)

Команда чтения из банка m прерывает запись в банк n, выходные данные появляются через CAS latency. Деактивация банка n начнётся через tWR, а отсчёт tWR начнётся, когда произойдёт чтение из банка m. Последняя правильная запись в банк n произойдёт за такт до чтения из банка m (рис. 26).

5.8.2.2. Прерывается записью (с автоматической деактивацией или без неё)

Запись в банк m прерывает запись в банк n. Деактивация банка n начнётся через tWR, а отсчёт tWR начнётся, когда произойдёт запись в банк m. Последние правильные данные будут записаны в банк n за один такт до записи в банк m (рис. 27).